RK3588J外接WiFi 5详解:BL-M8822CP1硬件设计实战

在高性能嵌入式系统设计中,Rockchip RK3588J 搭配 WiFi 5 模块是实现高速联网的标准方案。本文将结合 必联(B-Link)BL-M8822CP1 的实际原理图,深度解析其硬件接法与设计要点。

BL-M8822CP1 模块的核心采用了 Realtek(瑞昱)RTL8822CE 高性能芯片。该芯片是一款高度集成的单芯片解决方案,支持 2T2R 多输入多输出技术,兼容 802.11ac Wave 2 标准。它集成了射频、基带和物理层,支持 2.4GHz/5GHz 双频通讯,WiFi 理论速率高达 867Mbps。此外,该芯片单片集成了 蓝牙 5.0 控制器,支持多种低功耗模式,为 RK3588J 提供了极其稳定的无线扩展底座。

1. 核心接口与电源滤波设计

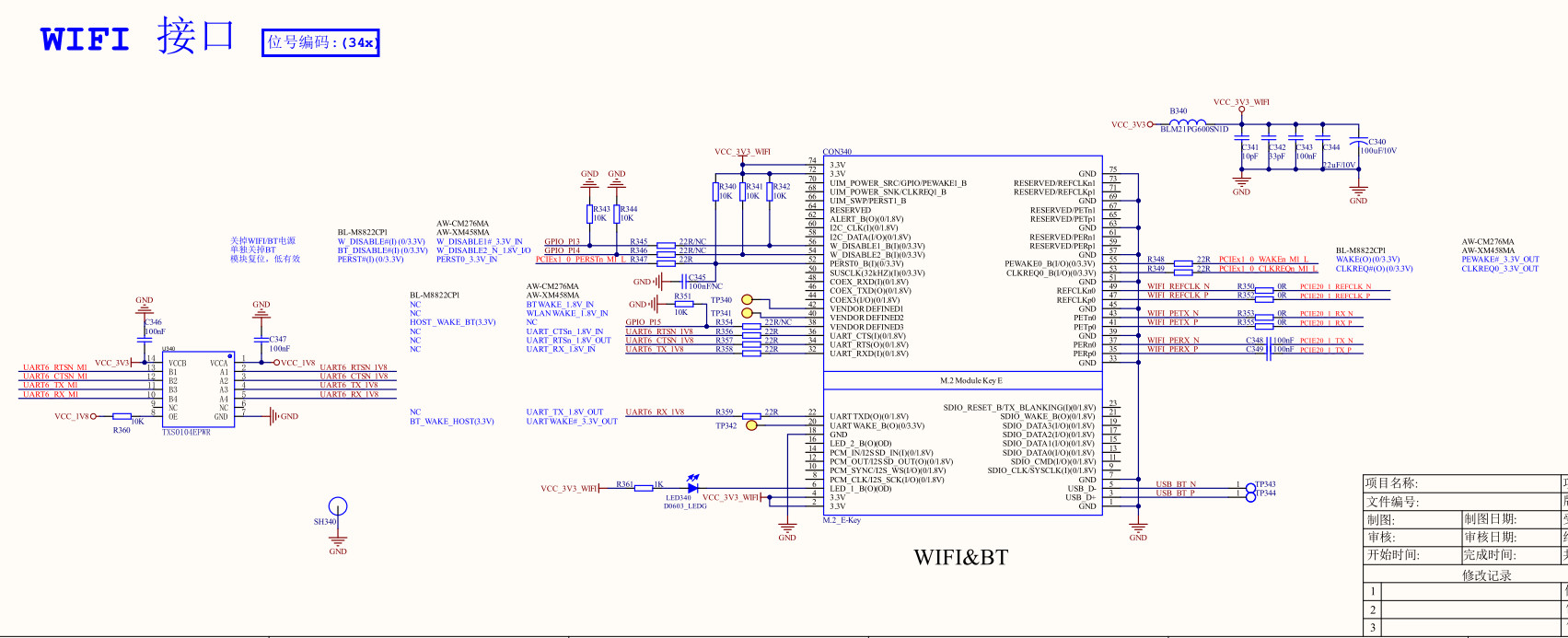

从原理图分析,BL-M8822CP1 采用标准的 M.2 Key E 接口。由于 RTL8822CE 在 5GHz 高频段高速发射时电流波动较大,电源纯净度直接影响信号的 EVM 指标。

●多级滤波: 原理图中 VCC_3V3_WIFI 采用了磁珠 B340 (BLM21PG600SN1D) 隔离系统噪声。

●电容阵列: 后级并联了 100uF + 22uF 大电容用于稳压,并辅以 100nF、33pF、10pF 小电容滤除不同频段的高频杂讯。这种“大到储能、小到避噪”的组合,是确保模块在高负载下不掉线的关键。

图一 RK3588接M.2 WIFI模块接法

2. PCIe 2.0 与 USB 信号链路

RK3588J 与模块间的高速通讯主要依靠 PCIe 总线(WiFi)和 USB 总线(蓝牙)。

●PCIe 差分对: WIFI_PETX/RX 链路必须严格控制 100Ω 差分阻抗。图中在 TX 发送端和参考时钟线上串接了 100nF 的交流耦合电容(C348/C349),这是防止直流偏置干扰、保护 SoC 接口的必要设计。

●蓝牙总线: 蓝牙部分走 USB 2.0 协议,差分信号 USB_BT_N/P 的阻抗应控制在 90Ω。

3. 实战避坑:电平转换与信号匹配

在原理图中可以注意到,设计者引入了 TXS0104EPWR (U340) 双向电平转换芯片。这是因为 RK3588J 的 UART 控制电平(通常为 1.8V)与模块电平(3.3V)不匹配,直接互连会导致系统不稳定。

weathink专业解决方案提供商 在处理工业级项目时,通常会强调以下细节:

●复位逻辑: PERST#(复位)信号应配合 SoC 的上电时序,建议在软件层增加 100ms 以上的延迟,待电源稳定后再拉高。

●射频走线: M.2 接口附近的 RF 走线应保持完整的参考地平面,严禁跨分割,以减少回损并提升穿墙性能。

4. 软件适配与状态监测

硬件连接完成后,RK3588J 需在 DTS(设备树)中配置相应的 PCIe 节点并加载 RTL8822CE 的固件。此外,原理图中的 LED340 指示灯(接 PIN 2/6)提供了直观的硬件心跳监测,方便在调试阶段判断模块是否成功初始化。

5. 总结

基于 RK3588J 与 BL-M8822CP1 的设计不仅是引脚的物理连接,更是对电源稳定性、阻抗匹配和逻辑电平的综合把控。针对复杂电磁环境下的稳定性需求,weathink专业解决方案提供商 建议在设计初期就进行完整的信号完整性评审,从而缩短产品的开发周期。

相关产品>

-

T153工控板

●CPU:T153,4核处理器,最高主频1 6GHz●MCU:600-MHz RISC-V E907●RAM:256MB 512MB 1GB DDR3●NAND:256MB 512MB NAND Flash●eM

了解详情

-

-

RK3588工控板

●CPU:Rockchip RK3588●架构:四核Cortex-A76 + 四核Cortex-A55●NPU:6TOPS●内存:4GB 8GB 16GB LPDDR4x●Flash:32GB

了解详情

-

瑞芯微RK3588核心板

●CPU:RK3588 RK3588J●架构:四核Cortex-A76 +四核Cortex-A55●NPU:6TOPS●RAM:4GB(默认) 8GB 16GB LPDDR4x●ROM:32GB(默认

了解详情

EN

EN