TI AM335X核心板

●CPU: AM3354

●架构: Cortex A8

●主频: 800MHZ

●内存: 128Mbyte

●Flash: 256Mbyte

●操作系统: Linux 3.12.0

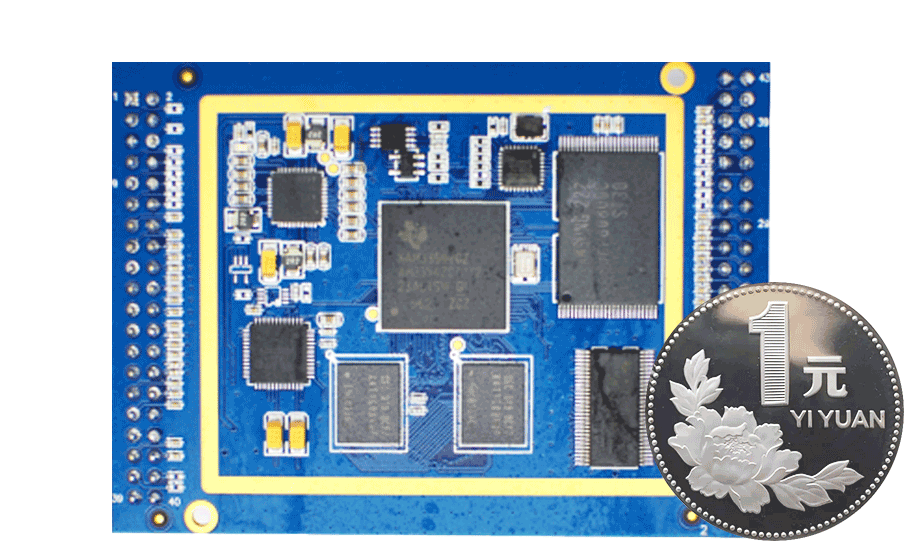

●接口方式: 邮票孔

- 概述特点

- 规格参数

- 资料下载

- 订购方式

-

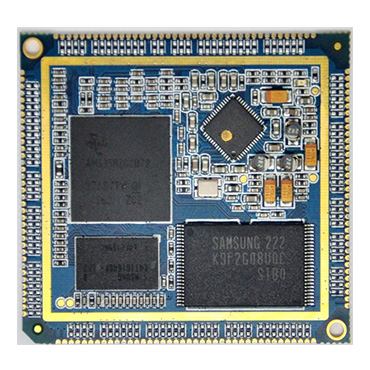

WTC-AM335X-D 核心板

WTC-AM335X-D核心板基于TI公司Sitara系列的工业级ARM处理器AM3354设计完成,ARM Cortex-A8架构,运行频率800MHz。核心板所有元器件均采用工业级用料,整板运行温度-40℃~+85℃。板载256MB的DDR2内存,存储采用256MB的SLCNandFlash存储芯片(1G容量可选),再搭配TI公司专为AM335X处理器配套设计的电源管理芯片TPS65910,使整板性能更加稳定。核心板资源丰富,共计160pin CPU引脚可根据功能需求实现不同扩展方式。

-

▊规格参数

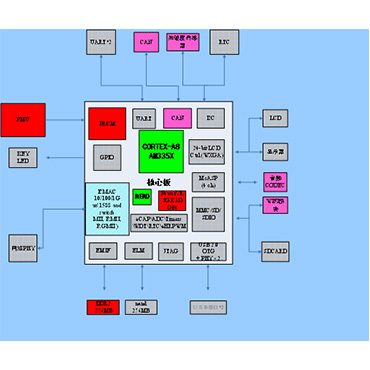

CPU

TI AM3354

架构

ARMv7 Cortex-A8

2D/3D

支持

图形处理器

PowerVR SGX530

UART

6路

LCD

24位RGB输出

CAN

2路

SPI

2路

I2C

3路

IIS

2路

ADC

8路

PWM

3路

Ethernet

2路MAC

VideoEncoder

软件编解码

SD/MMC/SDIO

3路MMC接口

USB OTG

1路USB OTG2.0

USB Device

1路 USB Device 2.0

-

▊资料下载

-

▊订购方式

WTC-3354S:AM3354 800MHZ,128MByte DDR,256MByte NAND

-

其它推荐:

EN

EN