瑞芯微 RK3588J 扩展 PCIe 3.0 x4 插槽原理图设计详解

瑞芯微 RK3588J 是一款具备强大算力与高性能接口的工业级 SoC。其内置的 PCIe 3.0 控制器支持多通道配置,最常见的应用方案便是通过其提供的 4 Lane 资源扩展为一个标准的 PCIe 3.0 x4 插槽。

基于你提供的参考原理图,本文将从高速数据连接、时钟分配、电源管理以及控制信号四个维度,解析 RK3588J 连接 PCIe 3.0 x4Lane 插槽的设计要点。

1、 高速信号连接 (High-Speed Data Lanes)

在 PCIe 3.0 设计中,差分信号的完整性是核心。RK3588J 的 PCIe 3.0 接口通常被分为两个控制器(Port 0 和 Port 1),在 x4 模式下,它们被合并使用。PCIe 3.0 x4 链路采用 8GT/s 的位速率,利用 128b/130b 编码极大提升了传输效率。其单通道双向带宽约为 2GB/s,x4 模式下总带宽可达 8GB/s。这种高带宽设计确保了 RK3588J 与高速外设间的海量数据交换。

●发送端 (TX): 信号从 RK3588J 发出,经过 220nF 的交流耦合电容(如图中的 C224、C225 等)连接至插槽。这是 PCIe 规范的强制要求,用于隔离直流电平。

●接收端 (RX): 信号从插槽直接连回 SoC。

●阻抗控制: 差分走线必须严格控制为 85Ω 或 100Ω(取决于 PCB 设计规范,通常 PCIe 建议 85Ω 以匹配连接器阻抗)。

图一 PCIe 4Lane 插槽

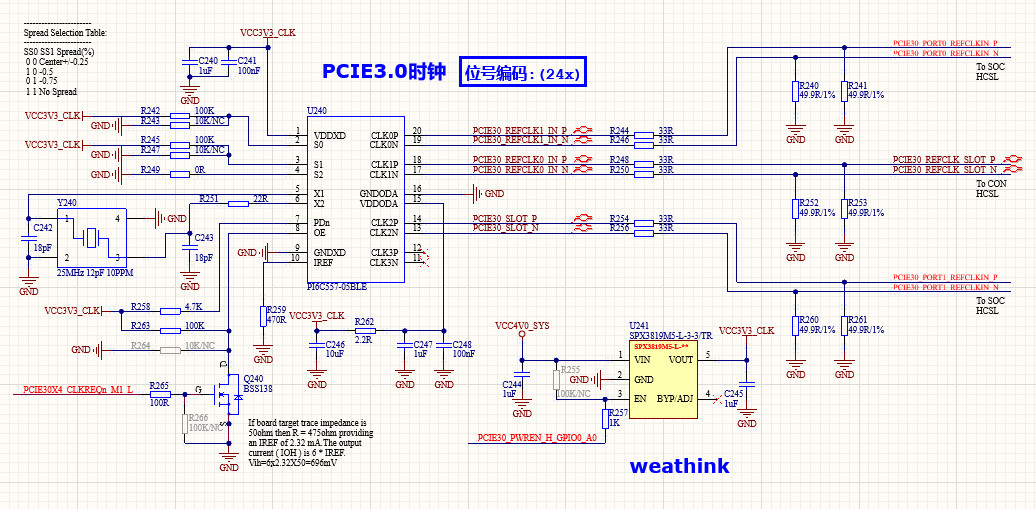

2、 时钟电路设计 (Clock Distribution)

PCIe 3.0 要求极其稳定的 100MHz 参考时钟(REFCLK)。

●时钟缓冲器 (Clock Buffer): 参考图中使用了一颗 PI6C557-05BLE 时钟驱动器。它将 25MHz 的晶振信号倍频并分配出多组差分 100MHz HCSL 电平信号。

●双向分发:

一组信号(REFCLK0)送往 RK3588J SoC 的 PCIe 时钟输入端。

另一组信号(REFCLK_SLOT)送往 PCIe 插槽 的 A13/A14 引脚。

●匹配电阻: 在时钟输出端,通常可见 33Ω 的串联匹配电阻(R244, R246 等)以及靠近接收端的 49.9Ω 接地电阻,以减少信号反射并确保 HCSL 电平正确。

图二 时钟电路

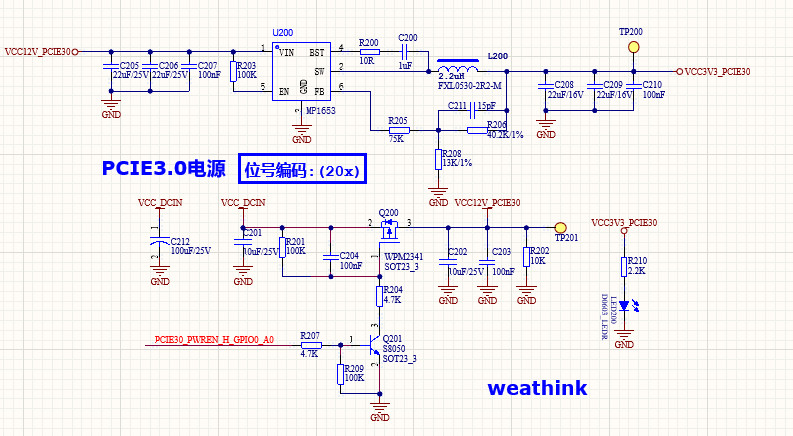

3、 电源管理与控制逻辑 (Power Management)

PCIe 插槽需要 12V 和 3.3V 电源,且通常需要受 SoC 控制以实现有序上电。

●DCDC 转换: 图中使用了 MP1653 等降压芯片,将主电源转换为 PCIe 所需的 VCC3V3_PCIE30。

●电源开关 (Power Enable): 通过 SoC 的 GPIO(如 GPIO0_A0)控制 MOS 管(Q200, Q201)来开启或关闭插槽电源。这对于低功耗管理和保护电路至关重要。

●去耦滤波: 在插槽电源引脚处配置了大容量电解电容(100uF/220uF)与瓷片电容组合,以应对插拔瞬间的浪涌电流。

图三 电源电路

4、 控制与辅助信号 (Control Signals)

除了高速数据线,以下信号对于 PCIe 链路的建立同样关键:

●PERST# (Reset): 复位信号。由 SoC 发出,经过电平转换(如 1.8V 转 3.3V)送往插槽。参考图中使用 C223 进行了简单的 RC 延时滤波,以确保复位释放时系统已稳定。

●WAKE#: 唤醒信号。支持设备从低功耗状态唤醒主机。

●PRSNT2# (Presence): 存在检测信号。该信号(如插槽的 B31 引脚)通常通过电阻上拉至 3.3V 并连接至 SoC 的 GPIO。当插卡插入时,该引脚接地,SoC 即可识别到设备已接入。

●CLKREQ#: 时钟请求信号。用于实现 L1 子状态下的时钟门控,节省功耗。

5、 设计注意事项

●等长约束: 差分对内等长应控制在 5mil 以内,对与对之间在 x4 模式下也需尽量保持等长,以减小偏斜。

●完整地平面: 高速信号线下严禁跨分割,必须拥有完整的参考地平面。

●ESD 保护: 在工业级设计中,建议在 PCIe 插槽的信号线上靠近连接器处增加低电容的 ESD 保护器件。

通过以上设计,RK3588J 可以稳定驱动各类 PCIe 3.0 设备,如 NVMe 固态硬盘、万兆网卡或 FPGA 采集卡。

6、 采用 Weathink WTC-RK3588-B SOM 的优势

在实际开发中,直接基于 RK3588J 芯片进行全板设计面临极高挑战。采用 Weathink WTC-RK3588-B 核心板可显著加速进程

●简化设计: 核心板集成了 CPU、DDR 及电源管理,开发者仅需参考 图一 Connect.jpg 设计基础底板,大幅降低 PCB 层数与成本。

●性能保障: 核心板已完成最复杂的阻抗匹配与信号仿真,确保 PCIe 3.0 在 8Gbps 下稳定运行。

●缩短周期: 结合成熟的时钟方案与 电源架构,可跳过核心系统调试,使产品快速上市。

相关产品>

-

T153工控板

●CPU:T153,4核处理器,最高主频1 6GHz●MCU:600-MHz RISC-V E907●RAM:256MB 512MB 1GB DDR3●NAND:256MB 512MB NAND Flash●eM

了解详情

-

-

RK3588工控板

●CPU:Rockchip RK3588●架构:四核Cortex-A76 + 四核Cortex-A55●NPU:6TOPS●内存:4GB 8GB 16GB LPDDR4x●Flash:32GB

了解详情

-

瑞芯微RK3588核心板

●CPU:RK3588 RK3588J●架构:四核Cortex-A76 +四核Cortex-A55●NPU:6TOPS●RAM:4GB(默认) 8GB 16GB LPDDR4x●ROM:32GB(默认

了解详情

EN

EN