RK3568核心板设备树配置LVDS液晶屏驱动技术指南

摘要

本文详细介绍了瑞芯微RK3568处理器在Linux环境下,如何通过设备树(Device Tree)配置LVDS(Low-Voltage Differential Signaling)液晶屏驱动。我们将深入探讨LVDS接口的原理、设备树中的关键节点、时序参数配置以及常见问题排查,旨在为硬件和软件工程师提供一套完整且实用的配置指南,确保LVDS液晶屏在RK3568平台上稳定、高效地工作。

1. RK3568与LVDS液晶屏概述

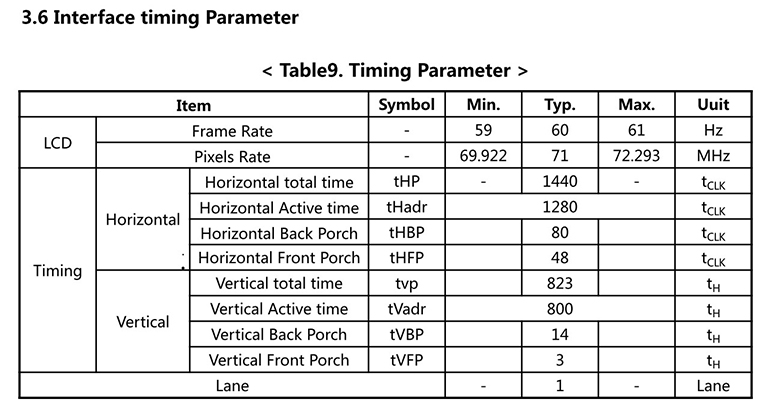

瑞芯微RK3568是一款高性能、低功耗的通用型SoC,广泛应用于智能NVR、云终端、IoT网关、工控平板等领域。它集成了强大的多媒体处理能力,支持多种显示接口,其中LVDS是工业和车载领域常用的显示接口,以其抗干扰能力强、传输距离远、功耗低等优点而备受青睐。LVDS液晶屏通过差分信号传输图像数据,需要精确的时序和正确的配置才能正常显示。在Linux系统中,设备树(Device Tree)是描述硬件信息的核心机制,对于RK3568这类复杂的SoC,所有外设(包括显示控制器和LVDS接口)的配置都通过设备树来完成,下面基于WTC-RK3568核心板的硬件,采用BOE的一款液晶屏来做为例子来配置下,型号是EV101WXM,参数如下:

图一 液晶屏时序参数

2. 设备树配置基础

设备树是Linux内核用于描述硬件拓扑结构的数据结构。对于RK3568,其设备树文件通常位于内核源码的 arch/arm64/boot/dts/rockchip/ 目录下,例如 rk3568-evb.dts 或 rk3568-xxx-board.dts。配置LVDS液晶屏驱动,主要涉及以下几个方面:

●LVDS控制器配置:RK3568内部的LVDS控制器负责生成LVDS信号。

● LVDS PHY配置:LVDS物理层(PHY)负责将数字信号转换为LVDS差分信号。

● 面板(Panel)信息:描述所连接LVDS液晶屏的具体参数,包括分辨率、时序、背光控制等。

● 显示路由配置:确保显示数据正确地从RK3568内部显示控制器路由到LVDS输出。

3. LVDS设备树关键节点与属性配置

在RK3568的设备树中,LVDS液晶屏的配置通常涉及 &lvds 节点和 lvds-panel 子节点。

3.1 LVDS控制器节点 (&lvds)

这个节点主要配置LVDS控制器的工作模式和与面板的连接关系。

&lvds {

status = "okay"; // 使能LVDS控制器

ports {

#address-cells =<1>;

#size-cells =<0>;

port@1 {

reg =<1>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>; // 指向面板的输入端点

};

};

};

};

关键属性解释:

* status = "okay": 启用LVDS控制器。

* ports: 定义控制器与面板之间的连接关系。lvds_out_panel 是LVDS控制器的输出端点,它通过 remote-endpoint 指向面板的输入端点 panel_in_lvds。

3.2 LVDS PHY节点 (&lvds_phy)

LVDS PHY通常是RK3568内部的一个独立模块,负责LVDS信号的物理层特性。

&lvds_phy {

status = "okay"; // 使能LVDS PHY

rockchip,grf = <&grf>; // 引用GRF寄存器

rockchip,phy-supply = <&vcc_3v3>; // LVDS PHY的供电,根据实际原理图配置

};

关键属性解释:

* status = "okay": 启用LVDS PHY。

* rockchip,phy-supply: 指定LVDS PHY的供电电源。这需要根据你的硬件原理图来确定,确保电源节点正确引用。

3.3 面板(Panel)节点 (lvds-panel)

这是配置LVDS液晶屏核心参数的地方,包括分辨率、时序、背光、电源时序等。

lvds-panel {

compatible = "simple-panel"; // 通用面板兼容性

power-supply = <&vcc_3v3>; // 面板供电电源,根据实际原理图配置

backlight = <&backlight>; // 引用背光控制器节点

enable-gpios = <&gpio0 rk_pc5="" gpio_active_high="">; // 面板使能GPIO,根据实际原理图配置

// 面板电源/使能时序控制

prepare-delay-ms =<20>; // 面板准备(如供电)后的延时

enable-delay-ms =<20>; // 面板使能信号后的延时

disable-delay-ms =<20>; // 面板禁用信号后的延时

unprepare-delay-ms =<20>; // 面板去准备(如断电)前的延时

// LVDS总线数据格式

bus-format =; // 媒体总线格式,这里是RGB888,单通道7对差分线,4对控制线,SPWG标准

// 面板物理尺寸

width-mm =<217>; // 面板宽度(毫米)

height-mm =<136>; // 面板高度(毫米)

// 屏幕分辨率和时序参数 (重要!)

display-timings {

native-mode = <&timing0>; // 指定原生模式为timing0

timing0: timing0 {

// 像素时钟频率 (单位: Hz)

clock-frequency =<71000000>; // 例如,71MHz

// 水平时序

hactive =<1280>; // 水平有效像素

hback-porch =<80>; // 水平后沿

hfront-porch =<48>; // 水平前沿

hsync-len =<32>; // 水平同步脉冲宽度

hsync-active =<0>; // 水平同步信号极性 (0: 低有效, 1: 高有效)

// 垂直时序

vactive =<800>; // 垂直有效像素

vback-porch =<14>; // 垂直后沿

vfront-porch =<3>; // 垂直前沿

vsync-len =<6>; // 垂直同步脉冲宽度

vsync-active =<0>; // 垂直同步信号极性 (0: 低有效, 1: 高有效)

// 数据使能和像素时钟极性

de-active =<0>; // 数据使能信号极性 (0: 低有效, 1: 高有效)

pixelclk-active =<0>; // 像素时钟极性 (0: 下降沿, 1: 上升沿)

};

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>; // 指向LVDS控制器的输出端点

};

};

};

新增属性解释:

●prepare-delay-ms, enable-delay-ms, disable-delay-ms, unprepare-delay-ms: 这些是面板电源和使能时序的延时参数,用于确保面板在正确的时间上电、使能、禁用和断电,避免时序冲突导致显示异常。具体数值应参考液晶屏数据手册。

●bus-format =;: 这定义了LVDS总线上传输数据的格式。

●RGB888: 表示每个像素使用RGB 8位数据。

●1X7X4: 通常指单通道(1X),7对数据差分线(7X),4对控制差分线(4X)。这是一种非标准但常见的LVDS配置表示方式,具体含义需结合芯片手册和面板手册确认。

●SPWG: 可能指的是某种特定的LVDS标准或模式,如SPWG-LVDS。

● width-mm, height-mm: 面板的物理尺寸,用于系统计算DPI(每英寸点数)。

● de-active: 数据使能信号(Data Enable)的极性。

3.4 显示路由节点 (&lvds_in_vp1, &route_lvds)

这些节点负责RK3568内部显示数据路径的路由,确保图像数据从视频处理器正确地发送到LVDS控制器。

&lvds_in_vp1 {

status = "okay"; // 使能LVDS输入到视频处理器1的路由

};

&route_lvds {

status = "okay"; // 使能LVDS路由

charge_logo,mode = "center"; // 充电Logo显示模式,例如居中

connect = <&vp1_out_lvds>; // 连接到视频处理器1的LVDS输出

};

关键属性解释:

●&lvds_in_vp1: 表示LVDS信号输入到视频处理器1的路径。

●&route_lvds: 定义LVDS显示数据的具体路由方式,包括充电Logo的显示模式以及连接到哪个视频输出端口。

3.5 其他显示控制器状态 (&dsi0, &dsi1, &video_phy0, &video_phy1)

根据您的配置,其他MIPI DSI控制器被禁用,而特定的视频PHY被使能。

&dsi0 {

status = "disabled"; // 禁用DSI0控制器

};

&dsi1 {

status = "disabled"; // 禁用DSI1控制器

};

&video_phy0 {

status = "okay"; // 使能视频PHY0

};

&video_phy1 {

status = "disabled"; // 禁用视频PHY1

};

关键属性解释:

● &dsi0, &dsi1: 明确禁用MIPI DSI控制器,这表明LVDS输出不是通过DSI控制器切换模式实现,而是通过独立的LVDS控制器 (&lvds)。

● &video_phy0, &video_phy1: 控制视频物理层接口的状态。video_phy0 的使能通常与LVDS输出路径相关。

4. 背光(Backlight)配置

LVDS液晶屏通常需要独立的背光控制。RK3568可以通过PWM或GPIO来控制背光亮度。

4.1 PWM背光控制

&pwm5 { // 使用PWM5控制器

status = "okay";

};

backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm5 0="" 25000="">; // PWM5通道0, 周期25000ns (40KHz), 极性0 (正常)

brightness-levels = <

0 20 20 21 21 22 22 23 23 24 24 25 25 26 26 27

27 28 28 29 29 30 30 31 31 32 32 33 33 34 34 35

35 36 36 37 37 38 38 39 40 41 42 43 44 45 46 47

48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95

96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111

112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127

128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143

144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159

160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175

176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191

192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207

208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223

224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239

240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255

>; // 亮度等级

default-brightness-level =<200>; // 默认亮度

post-pwm-on-delay-ms =<10>; // PWM开启后的延时

pwm-off-delay-ms =<10>; // PWM关闭前的延时

status = "okay";

};

新增属性解释:

● post-pwm-on-delay-ms: PWM开启后的延时,用于确保背光控制器稳定后再进行其他操作。

● pwm-off-delay-ms: PWM关闭前的延时,用于确保背光平稳关闭。

4.2 GPIO背光控制

如果背光只是简单的开关控制,可以使用GPIO。

backlight: backlight {

compatible = "gpio-backlight";

gpios = <&gpio0 rk_pb1="" gpio_active_high="">; // 背光控制GPIO

default-on; // 默认开启背光

status = "okay";

};

5. 完整设备树示例 (基于您提供的配置)

以下是根据您提供的配置片段整理的RK3568设备树示例。请注意,这仍然是一个片段,需要集成到您的主设备树文件(如 rk3568-xxx-board.dts)中。

// 在你的rk3568-xxx-board.dts或rk3568.dtsi中添加或修改

#include// 包含GPIO定义

#include// 包含媒体总线格式定义

&grf {

// 可能需要配置一些LVDS相关的GRF寄存器

// 例如,LVDS PHY的IO复用等

};

&lvds {

status = "okay";

ports {

#address-cells =<1>;

#size-cells =<0>;

port@1 {

reg =<1>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>;

};

};

};

};

&lvds_phy {

status = "okay";

rockchip,grf = <&grf>;

rockchip,phy-supply = <&vcc_3v3>; // 假设LVDS PHY由3.3V供电

};

// 假设vcc_3v3是你的3.3V电源节点,如果不是,请根据实际原理图修改

&vcc_3v3 {

regulator-name = "vcc_3v3";

regulator-always-on;

regulator-boot-on;

status = "okay";

};

&pwm5 { // 使用PWM5控制器控制背光

status = "okay";

};

lvds-panel {

compatible = "simple-panel";

power-supply = <&vcc_3v3>; // 面板供电电源

backlight = <&backlight>;

enable-gpios = <&gpio0 rk_pc5="" gpio_active_high="">; // 面板使能GPIO为GPIO0_PC5

prepare-delay-ms =<20>;

enable-delay-ms =<20>;

disable-delay-ms =<20>;

unprepare-delay-ms =<20>;

bus-format =;

width-mm =<217>;

height-mm =<136>;

// BOE,EV101WXM-N10

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency =<71000000>;

hactive =<1280>;

vactive =<800>;

hback-porch =<80>;

hfront-porch =<48>;

vback-porch =<14>;

vfront-porch =<3>;

hsync-len =<32>;

vsync-len =<6>;

hsync-active =<0>; // 低有效

vsync-active =<0>; // 低有效

de-active =<0>; // 低有效

pixelclk-active =<0>; // 下降沿有效

};

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>;

};

};

};

backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm5 0="" 25000="">; // PWM5通道0, 周期25000ns (40KHz), 极性0 (正常)

brightness-levels = <

0 20 20 21 21 22 22 23 23 24 24 25 25 26 26 27

27 28 28 29 29 30 30 31 31 32 32 33 33 34 34 35

35 36 36 37 37 38 38 39 40 41 42 43 44 45 46 47

48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95

96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111

112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127

128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143

144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159

160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175

176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191

192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207

208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223

224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239

240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255

>;

default-brightness-level =<200>;

post-pwm-on-delay-ms =<10>;

pwm-off-delay-ms =<10>;

status = "okay";

};

&lvds_in_vp1 {

status = "okay";

};

&route_lvds {

status = "okay";

charge_logo,mode = "center";

connect = <&vp1_out_lvds>;

};

&dsi0 {

status = "disabled";

};

&dsi1 {

status = "disabled";

};

&video_phy0 {

status = "okay";

};

&video_phy1 {

status = "disabled";

};

6. 编译与烧录设备树

完成设备树修改后,需要重新编译设备树并烧录到RK3568设备中。

7. 总结

通过本文的详细介绍,相信您对RK3568设备树配置LVDS液晶屏驱动有了更深入的理解。核心在于精确匹配液晶屏数据手册中的时序参数,并正确配置RK3568内部的LVDS控制器和PHY以及显示路由。在实际开发中,采用Weathink RK3568核心板可以极大地简化硬件复杂度,让您更专注于软件配置和调试。耐心细致的排查和对硬件的深刻理解是成功的关键。希望这份指南能帮助您顺利点亮LVDS液晶屏,加速您的RK3568项目开发进程。

如果您在项目开发过程中,对RK3568硬件设计、LVDS液晶屏驱动或Weathink核心板有任何疑问,需要更深入的技术支持或定制化服务,欢迎随时联系我们:

联系人: 林伟

邮箱: lw@weathink.com

电话: 18072728558

相关产品>

-

T153工控板

●CPU:T153,4核处理器,最高主频1 6GHz●MCU:600-MHz RISC-V E907●RAM:256MB 512MB 1GB DDR3●NAND:256MB 512MB NAND Flash●eM

了解详情

-

-

RK3588工控板

●CPU:Rockchip RK3588●架构:四核Cortex-A76 + 四核Cortex-A55●NPU:6TOPS●内存:4GB 8GB 16GB LPDDR4x●Flash:32GB

了解详情

-

瑞芯微RK3588核心板

●CPU:RK3588 RK3588J●架构:四核Cortex-A76 +四核Cortex-A55●NPU:6TOPS●RAM:4GB(默认) 8GB 16GB LPDDR4x●ROM:32GB(默认

了解详情

EN

EN